## Intel/HP EPIC/IA-64 Architecture

55:132/22C:160 High Performance Computer Architecture

Conviolst 2001 James C. Hoe CMII and John P. Shen Inte

## Intel/HP EPIC/IA-64 Architecture

- EPIC (Explicitly Parallel Instruction Computing)

- An ISA philosophy/approach

e.g. CISC, RISC, VLIW

- Very closely related to but not the same as VLIW

- ◆ IA-64

- An ISA definition

e.g. IA-32 (was called x86), PA-RISC

- Intel's new 64-bit ISA

- An EPIC type ISA

- Itanium (was code named Merced)

- A processor implementation of an ISA

e.g. P6, PA8500

- The first implementation of the IA-64 ISA

Copyright 2001, James C. Hoe, CMU and John P. Shen, Inte

#### IA-64 Architecture

- 128 general-purpose registers

- 128 floating-point registers

- Arbitrary number of functional units

- Arbitrary latencies on the functional units

- Arbitrary number of memory ports

- Arbitrary implementation of the memory hierarchy

Needs retargetable compiler and recompilation to achieve maximum program performance on different IA-64 implementations

Copyright 2001 James C. Hoe CMU and John P. Shen. In

#### IA-64 Instruction Format

- ◆ IA-64 "Bundle"

- Total of 128 bits

- Contains three IA-64 instructions (aka syllables)

- Template bits in each bundle specify dependencies both within a bundle as well as between sequential bundles

- A collection of independent bundles forms a "group"

A more efficient and flexible way to encode ILP then a fixed VLIW format

- IA-64 Instruction

- Fixed-length 40 bits long

- Contains three 7-bit register specifiers

- Contains a 6-bit field for specifying one of the 64 one-bit predicate registers

Copyright 2001, James C. Hoe, CMU and John P. Shen, In

#### IA-64 EPIC vs. Classic VLIW

- Similarities:

- Compiler generated wide instructions

- Static detection of dependencies

- ILP encoded in the binary (a group)

- Large number of architected registers

- Differences:

- Instructions in a bundle can have dependencies

- Hardware interlock between dependent instructions

- Accommodates varying number of functional units and latencies

- Allows dynamic scheduling and functional unit binding Static scheduling are "suggestive" rather than absolute

- ⇒Code compatibility across generations

but software won't run at top speed until it is recompiled so "shrink-wrap binary" might need to include multiple builds

Copyright 2001, James C. Hoe, CMU and John P. Shen, Int.

#### Additional Features of IA64

- Predicated execution

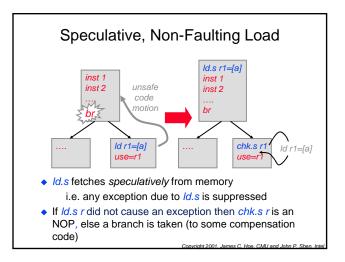

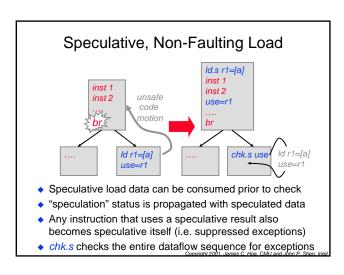

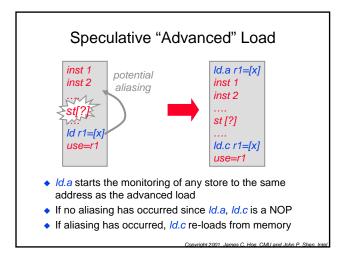

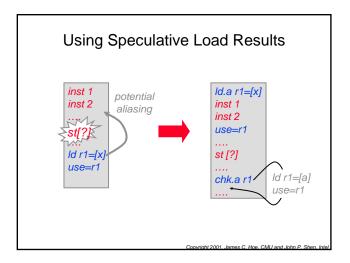

- Speculative, non-faulting Load instruction

- Software-assisted branch prediction

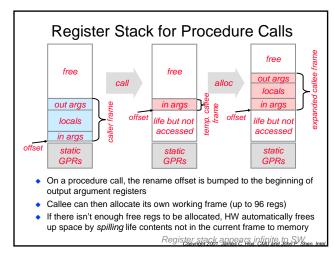

- Register stack

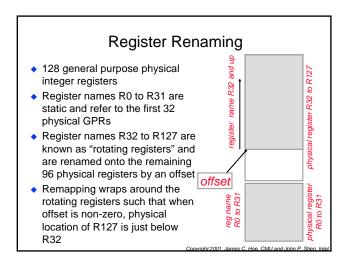

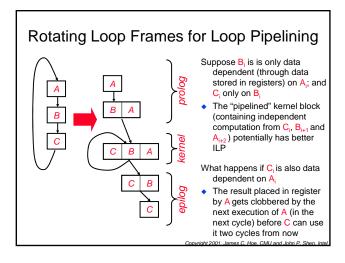

- Rotating register frame

- Software-assisted memory hierarchy

See "Understanding the IA-64 Architecture" by G. Doshi, Intel

Copyright 2001, James C. Hoe, CMU and John P. Shen, Int.

#

#### **Branch Prediction**

- Static branch hints can be encoded with every branch

- taken vs. not-taken

- whether to allocate an entry in the dynamic BP hardware

- SW and HW have joint control of BP hardware

- "brp" (branch prediction) instruction can be issued ahead of the actual branch to preset the contents of BPT and BTAC Itanium uses a 512-entry 2-level BPT and 64-entry BTAC

- TAR (Target Address Register)

- a small, fully-associative BTAC-like structure

- contents are controlled entirely by a "prepare-to-branch" inst.

- a hit in TAR overrides all other predictions

- RSB (Return Address Stack)

- Procedure return addr is pushed (or popped) when a procedure is called (or when it returns)

- Predicts nPC when executing register-indirect branches

Copyright 2001 James C. Hoe. CMU and John P. Shen, Int.

```

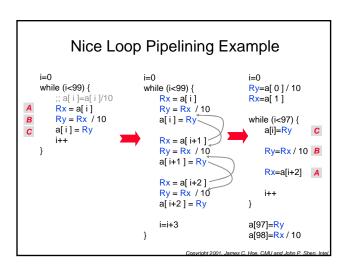

Loop Pipelining Requiring Renaming

i=0

Ry=a[ 0 ] / 10

Rx=a[ 1 ]

i=0

i=0

while (i<99) {

while (i<99) {

;; a[i]=a[i]/10+a[i]

Rx = a[i]

Rx = a[i]

Ry = Rx / 10

Ry = Rx / 10

while (i<97) {

a[i] = Ry + Rx

a[i]=Ry+Rx'

C

a[i] = Ry+Rx

WAR

Rx = a[i+1]

Ry=Rx/10

Ry = Rx / 10

a[i+1] = Ry+Rx

Rx'=Rx

Rx=a[i+2]

Rx = a[i+2]

Ry = Rx / 10

a[i+2] = Ry+Rx

a[97]=Ry + Rx'

}

a[98]=Rx / 10 + Rx

```

```

Renaming with Rotating Registers

i=0

Ry=a[ 0 ] / 10

i= -2

Rx=a[1]

while (i<99) {

pred(i>-1):

while (i<97) {

a[i]=Ry+Rx

a[i]=Ry+RR(x-2)

pred(i>-2 && i<98):

Ry=Rx / 10

Ry=RR(x-1)/10

Rx'=Rx

pred(i<97):

Rx=a[i+2]

RR(x)=a[i+2]

'increase RR offset by 1'

a[97]=Ry + Rx'

a[98]=Rx / 10 + Rx

```

# Itanium Specifics

- 6-wide 10-stage pipeline

- Fetch 2 bundles per cycle with the help of BP into a 8-bundle deep fetch queue

- 512-entry 2-level BPT, 64-entry BTAC, 4 TAR, and a RSB

- Issue up to 2 bundles per cycle some mixes of 6 instructions e.g. (MFI,MFI) or (MIB,MIB<sub>n</sub>)

- Can issue as little as one syllable per cycle on RAW hazard interlock or structural hazard (scoreboard for RAW detection)

- 8R-6W 128 Entry Int. GPR, 128 82-bit FPR, 64 predicate reg's

- 4 globally-bypassed single-cycle integer ALUs with MMX, 2 FMACs, 2 LSUs, 3 BUs

- ◆ Can execute IA-32 software directly

- Intended for high-end server and workstations

opyright 2001 James C. Hoe. CMI and John P. Shen. Inte

|        | Itanium Per                                                     | formance                     |              |                |

|--------|-----------------------------------------------------------------|------------------------------|--------------|----------------|

|        |                                                                 | SPEC2000                     |              |                |

| system |                                                                 | int                          | fp           |                |

|        | hp workstation i2000<br>800MHz, 2-way, 2MB cache,<br>Windows XP |                              | 658          |                |

|        | hp workstation i2000<br>800MHz, 1-way, 2MB cache,<br>HP-UX      | 365*                         | 610*         |                |

|        | hp workstation i2000<br>733MHz, 1-way, 2MB cache,<br>Windows XP |                              | 623          |                |

|        | hp workstation i2000<br>733MHz, 1-way, 2MB cache,<br>HP-UX      | 335*                         | 577*         |                |

|        |                                                                 | Copyright 2001, James C. Hoe | e CMU and Jo | hn P. Shen. li |

| How does                                        | How does it compare?    |                    |  |  |  |

|-------------------------------------------------|-------------------------|--------------------|--|--|--|

|                                                 | SPEC_rate2000<br>(peak) |                    |  |  |  |

| system                                          | int                     | fp                 |  |  |  |

| hp<br>workstation<br>x4000<br>uni-<br>processor | 6.36                    | 6.43               |  |  |  |

| hp<br>workstation<br>x4000<br>dual<br>processor | 11.70                   | 10.50              |  |  |  |

|                                                 | Copyright 2001. Jam     | es C. Hoe. CMU and |  |  |  |